在电子产品领域当中,芯片的重要性不言而喻,一款好的芯片对电子产品的品质起着决定性作用,正如苹果手机的芯片以及中国华为手机的麒麟芯片等,一个科技产品公司只有掌握了真正的核心科技,才能屹立在行业中,成为行业标杆。

而产品研发生产商打广告时,总是喜欢在芯片前面加上几nm,表示科技含量高,最常见的就是7nm。7nm 到底指的是什么呢?

芯片实际上是在硅片上制造的高度集成的电路,里面集成了数十亿个晶体管,要想将那么多的晶体管做到极小面积的硅片之上,就需要每个晶体管的体积足够小,电路的导线足够细,我们所讲的5nm或者7nm就是指晶体管的宽度或者叫做线宽(CD)。

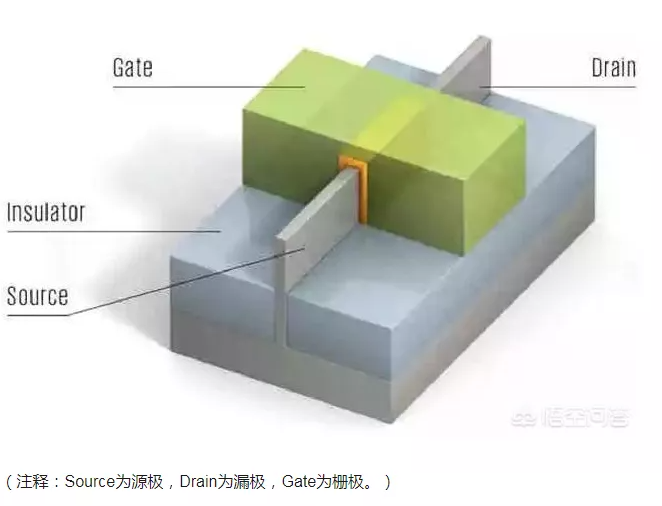

7nm芯片中的7nm也被称为栅长,简单来说指的是CPU的上形成的互补氧化物金属半导体场效应晶体管栅极的宽度为7nm。

电流从Source(源极)

流入Drain(漏级)

Gate(栅极)相当于闸门,主要负责控制两端源极和漏级的通断。

电流会损耗,而栅极的宽度则决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。而栅极的最小宽度(栅长),就是XX nm工艺中的数值。

芯片行业中制程工艺的每一次提升,带来的都是性能的增强和功耗的降低,而每一款旗舰手机的发布,常常与芯片性能的突破离不开关系。

7nm工艺制作难度

在量子力学里,量子隧穿效应指的是,像电子等微观粒子能够穿入或穿越位势垒的量子行为,尽管位势垒的高度大于粒子的总能量。在经典力学里,这是不可能发生的,但使用量子力学理论却可以给出合理解释。

如果通俗点来讲,就是说制程工艺到一定程度下,电路与电路之间的距离降低到一定程度就会出现量子隧穿效应,这些电子呈现的是一种我们所不知道的规律进行运动,于是这些不可控制的电子造成了半导体的漏电率急剧上升,有太多的能源被浪费在控制电子运动上,自然不能发挥晶体管应该有的性能,宏观上表现为处理器的发热量增加,但是性能没有太大的变化。因此,曾经也有媒体报道过7nm制程工艺最逼近硅基半导体工艺的物理极限。后来,媒体又报导,7nm工艺并非半导体工艺的极限,后面还依次有5nm工艺、3nm工艺,且5nm工艺、3nm工艺并没有突破硅材料半导体工艺的极限。

每一次升级都要打怪!

1号BOSS——光刻机(贼贵贼贵)

缩小晶体管真的是一个非常之艰难的事情。首先面临的难题就是光刻技术,就是说机器本身到底能不能准确的做出我想要的东西。如果看了介绍MOSFET的就知道,它是由硅衬底,掺杂形成的D端S端,金属加上氧化物的G端组成的,想要做出来一个晶体管要解决的一个问题就是我怎么能把这些材料放在他该放的地方,这就是光刻想要解决的问题。

2号BOSS——晶体管的结构

对于一个理想的晶体管,我希望在我的电压低于阀值电压时,他关的死死的,也就是漏电电流是0,但是当我的电压高于阀值电压的时候,电流瞬间饱和(特别像家长理想中的孩子,上学的时候就乖乖听话,毕业当天即刻长大)。

摩尔定律不是定律,而是机遇!

尽管这种趋势已经持续了超过半个世纪,摩尔定律仍应该被认为是观测或推测,而不是一个物理或自然法。预计定律将持续到至少2015年或2020年(也就是今年台积电研发2nm成就了新摩尔定律)。

芯片领域从10nm过渡到7nm,进而逐渐迈向2nm,每一次进步都伴随着芯片性能的极大提升,据计算,芯片每前进1nm,性能将提升30%-60%,尺寸越小意味着在相同的面积之内可以储存更多的晶体管,从而达到快的运行速度,进而也可以降低能耗。

国内热线:188 2581 2467

海外热线:188 2589 8464

技术支持:188 2581 0427